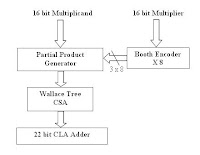

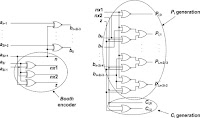

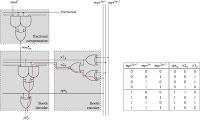

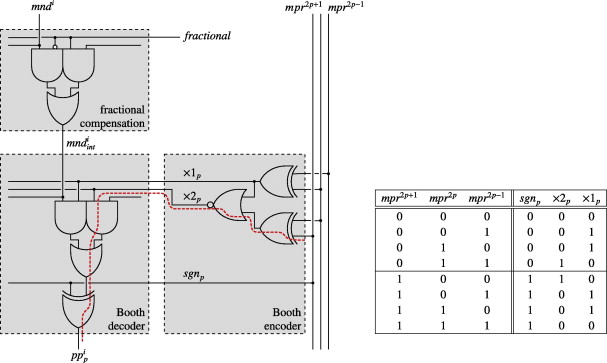

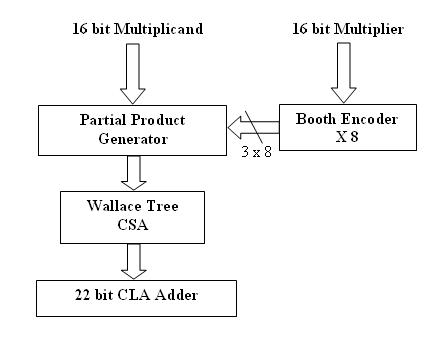

On the design of low power BIST for multipliers with Booth encoding and Wallace tree summation ☆ Dimitris Bakalis, Author Vitae, Emmanouil Kalligeros Author Vitae, Page 3 of 20 Abstract: In this project, we are building up a Modified Booth Encoding Radix-4 8-bit Multiplier using 0.5um CMOS technology. 2 B. Baas, © 2011 EEC 281 67 Booth Encoding—Non-Booth Yi Partial product 00 1+x [Waser and Flynn] •Simplest partial products • Look at one bit of multiplier Multiplier design with carry-save adder + Booth encoding: pallav: 10/5/09 10:32 AM: Hi, For fun, I'm trying to code up a 32x32 multiplier (R = X*Y) using 4 layers of CiteSeerX - Scientific documents that cite the following paper: Improved-Booth encoding for low-power multipliers CiteSeerX - Scientific documents that cite the following paper: A high speed and low power VLSI multiplier using a redundant binary Booth encoding I have not looked at a carry save implementation, but I don't think that would matter. IIRC, Booths algorithm automatically handles signed numbers because of the This paper shows that a simple modification to the Booth-encoding algorithm can be used to increase the probability of a zero coded digit. This increases the

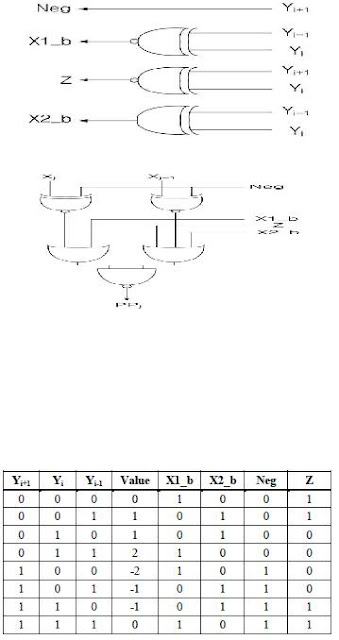

Booth Encoding

The latest patent applications on related to Pcod en-us Thu, 15 Aug 2013 19:43:34 -0700 1000 1192. IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I: REGULAR PAPERS, VOL. 56, NO. 6, JUNE 2009 A New Redundant Binary Booth Encoding for Fast 2n-Bit Multiplier Design

Booth Encoding

Booth Encoding

Booth Encoding

Booth Encoding

ไม่มีความคิดเห็น:

แสดงความคิดเห็น